App4

KDEV

PikeOS for MPU Kernel

PSP

Cortex-R52

App3

# **PikeOS for MPU 1.1**

# **Real-Time Partitioning OS for MPU Processor Architectures**

Consolidation

new range of controllers targeted to Aeronautics, Space, Automotive, and Medical applications.

eyego The separation kernel provides multiple, safely isolated partitions, which may contain different applications with different Safety / Security levels

MPU-based SoC

Connectivity

App2

KDEV

Memory Interface

PikeOS for MPU Kernel

PSP

The classic PikeOS is a real-time operating system including a separation kernel designed for the highest levels of Safety & Security. Its technology has been certified on a wide range of projects by various certification MPU standards including DO-178C, IEC 61508, EN 50128 / EN 50657, and ISO 26262. However, PikeOS needs hardware support by means of a Memory Management Unit (MMU). With PikeOS for MPU, the requirements have been lowered and architectures that come with less complicated MPUs are supported. This opens the gates for a

App1

ASP

FPGA

#### **CUSTOMER BENEFITS & USE CASES**

PikeOS for MPU is based on a separation kernel with the performance of a traditional real-time operating system. It provides partitions that can host different applications from a simple yet highly critical control task to a full Avionics partition.

#### Safety

Strict time and resource partitioning of the classic PikeOS separation kernel prevents application failures from propagating to any other place in the system.

#### **Advanced Scheduling Support**

PikeOS for MPU incorporates a hard real-time scheduler being fully ARINC 653 compliant. It is possible to switch between multiple pre-configured time partition scheduling schemes to optimise CPU usage based on the platform operating mode.

#### **Health Monitoring**

PikeOS for MPU provides built-in health monitoring functions, which implement all features described in the ARINC 653 standard. Application errors as well as hardware failures are intercepted by the OS and handled according to system and partitions specific configuration. This ensures a predictable system behaviour.

#### **Aeronautics & Space**

- · Onboard satellite software

- Flight control solutions (e.g. drones)

- · Electronic motor control

#### **Medical & Healthcare**

- · Wearable devices

- Infusion pumps

- Medical robots

#### **Automotive**

- · General functional Safety applications according to ISO 26262 ASIL D (e.g. airbag control)

- Tachograph application

- · Body control unit

#### **Industrial Automation**

· E.g. PLC control

## **Security**

- · HSM management

- · Building a secure boot process

### **DEVELOPMENT & CONFIGURATION TOOL**

CODEO is an Eclipse-based IDE and offers a complete environment for embedded systems covering the whole development cycle from early simulation and emulation tools to software update mechanisms for deployed systems.

Learn more: www.sysgo.com/codeo

#### **PIKEOS FOR MPU FEATURES**

- RTOS and separation kernel-based hard real-time operating system

- · Robust time & resource partitioning

- AMP multi-core processor support

- · Hardware abstraction

- First level exception and interrupt processing

- · Thread management & scheduling

- · Health monitoring

- Inter-partition communication and synchronisation

- ICCOM (Inter-Core Communication)

- I/O device abstraction and access control

- · CODEO, Eclipse-based IDE

- PikeOS compatibility

- Large software & hardware eco system

TRAININGS, CONSULTING & SUPPORT

www.sysgo.com/service

#### **PIKEOS FOR MPU: LIGHTWEIGHT RTOS**

PikeOS for MPU bases on the well-established operating system PikeOS, but at the same time allows the execution on systems that do not have an MMU. Still, the relationship between PikeOS and PikeOS for MPU is very strong. During the development of PikeOS for MPU more than 80% of the original code base had been reused, making the available PikeOS documentation and certification artefacts re-usable. In the future, the bonding between the two OS will be kept alive and improvements on one OS will be benefit to the other one.

PikeOS for MPU uses the same space and time partitioning mechanisms, but has some simplifications that are more adequate to simple controller systems. For example, features that require virtual memory management, such as memory pools or memory regions have been removed. This reduces complexity and moves the use cases closer to Space and Avionics use cases. Also, the overall complex task and address management has been discarded, as complex guest operating systems like Linux are not available on architectures with an MPU only. As a consequence, there is only one address space per resource partition, which brings the configuration of PikeOS for MPU closer to the original ARINC 653 specification.

No modifications have been made regarding the dynamic thread management; synchronisation primitives such as mutexes, semaphores, condition variables, atomic operations and PikeOS events are available. Interrupt and exception handling can be managed at user-level, similar to the original PikeOS philosophy. The ARINC 653 compatible inter partition communication has been left unchanged, offering queuing- and sampling ports. PikeOS for MPU allows the implementation of drivers in the kernel space through the PikeOS kernel driver development kit (KDEV).

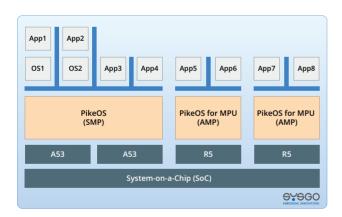

#### PIKEOS AND PIKEOS FOR MPU

Figure 1: PikeOS and PikeOS for MPU working hand in hand

Multi-core processors have entered the embedded market. However, unlike to desktop computing where all processor cores are of the same type, embedded SoCs (Systems-on-a-Chip) are highly specialized for a dedicated purpose.

Therefore, you will often find heterogeneous processor cores on the same chip. With the PikeOS product family, you can manage the entire software stack of such a complex big SoC within one single CODEO workspace. The project wizards and editors support you while you are planning the architecture of AMP and SMP domains. Even anything in between can be designed.

Fig. 1 shows a typical setup on a Xilinx Ultrascale+: PikeOS running multiple partitions on the Cortex-A53 cores in SMP mode, while the Cortex-R5 cores are executing PikeOS for MPU in AMP mode. The PikeOS instances running on different cores can communicate with each other via message-based communication channels by means of the ICCOM (Inter-Core Communication) component.

During your development it might turn out that the current assignment of software applications to processor cores is not optimal. Fortunately, this can be fixed with almost no effort, as the PikeOS solution allows to utilize a compatible API, no matter whether the CPU provides an MMU or MPU.

Founded in 1991, SYSGO became a trusted advisor for Embedded Operating Systems and is the European leader in hypervisor-based OS technology offering worldwide product life cycle support. We are well positioned to meet customer needs in all industries and offer tailor-made solutions with highest expectations in Safety & Security. More information at www.sysgo.com/pikeos-mpu

SYSGO Headquarters

**SYSGO France** +33 1 30 09 12 70 SYSGO Czech Republic +420 222 138 111

sales@sysgo.com

www.sysgo.com